[ad_1]

I’m at the moment growing a filtering undertaking utilizing MAX 10 FPGA and Quartus Prime 17.1 improvement software program。The filter is ready to make use of the fir ii IP core to filter out frequencies above 500Hz.

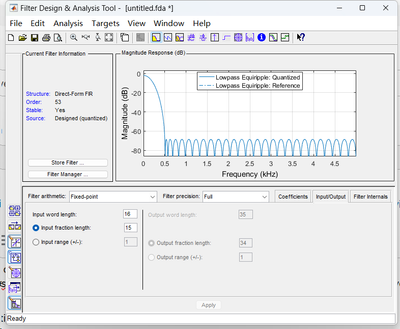

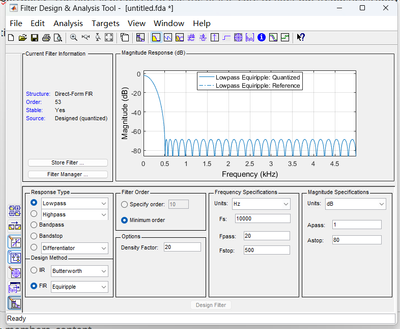

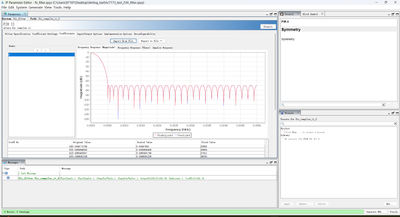

That is my setting in Matlab:

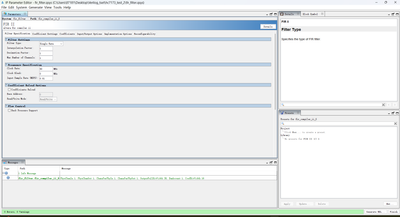

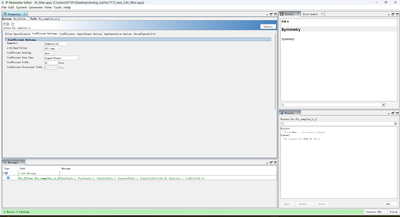

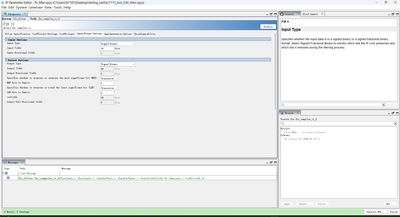

That is my setting within the fir ii IP core:

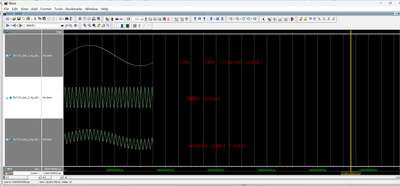

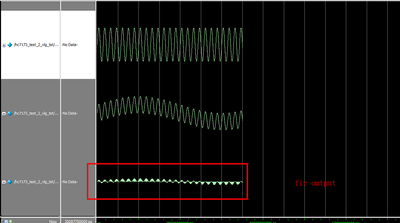

I’ve checked all of the settings, however the output of the simulation may be very unusual. Right here is my simulation consequence:

This drawback has been bothering me for a very long time and I have never discovered an answer. I hope the group can provide me some solutions

[ad_2]