[ad_1]

Hello all,

I’ve a design the place I generate an SPI clock and ship some knowledge over the slave. The slave is an ADC with its personal setup/maintain time constraints. In these constraints, the slave knowledge enter SDI has constraints with respect to the SCLK, however I am unsure tips on how to correctly constraint that. What I did to date is that I constrainted the SCLK by itself as if it is a knowledge output of the FPGA after which constraint the MOSI with referencing the SCLK. The syntax I used within the sdc file is added under.

# fundamental clock of the FPGA

create_clock -name {clk} -period 100MHz [get_ports {clk}]

# Specify generated clock from PLL (PLL output is 100MHz)

# set_instance_assignment -name corepll_inst|altpll_component|auto_generated|pll1 -to pll_inst

# create_generated_clock -name {pll_clk} -source [get_pins pll_inst|clk[0]] -divide_by 1

# constraints for SCLK and MOSI

set_output_delay -clock pll1 -max 3 [get_ports {SCLK1}]

set_output_delay -clock pll1 -min -2 [get_ports {SCLK1}]

set_output_delay -clock pll1 -reference_pin SCLK1 -max 5 [get_ports {MOSI1}]

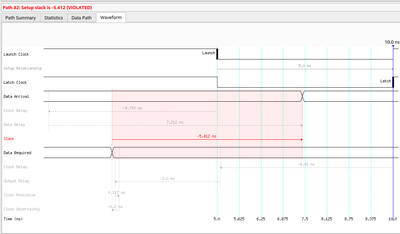

set_output_delay -clock pll1 -reference_pin SCLK1 -min -5 [get_ports {MOSI1}]What I observe within the Timing Analyzer is that the setup and maintain occasions should not the one issues when checking the timing analyzer. For the instance you can see on the snippet hooked up, I’d anticipate that the information required for the setup time of SCLK1 can be solely 3 ns removed from the latch clock’s posedge, the place the cursor is. I am nearly certain that what I need to obtain doesn’t match with the constraints I used, subsequently I would prefer to ask what I am doing fallacious or lacking.

Any assist is way appreciated,

Cheers

[ad_2]