[ad_1]

Hello,

I attempted to run gzip undertaking on OneAPI Devcloud. Right here is the supply code :

I exploit these following steps to run gzip on {hardware}:

Create a build_fpga.sh file within the listing with the next strains to compile and run the vector-add pattern:

Constructing the vector-add pattern for Stratix10 FPGA card:

mkdir construct

cd buid cmake ..

-DFPGA_DEVICE=intel_s10sx_pac:pac_s10

make fpga

As soon as the build_fpga.sh file is created, we submit the job to a Stratix10 node utilizing the beneath command:

qsub -l nodes=1:stratix10:ppn=2 -d . -l walltime=24:00:00 build_fpga.sh

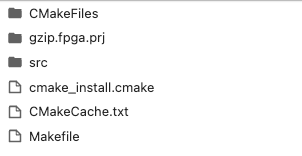

Sadly, .fpga. prj folder is generated, .fpga file shouldn’t be generated. How you can generated .fpga file?

build_fpga.sh.e2515172:

Error: unable to totally generate static experiences for this compile!Error: unable to totally generate static experiences for this compile!Warning: couldn’t collect details about the quartus compile for the static experiences!

Could not open file experiences/assets/json/quartus.json for studying

llvm-foreach:

icpx: error: fpga compiler command failed with exit code 42 (use -v to see invocation)

icpx: observe: diagnostic msg: The FPGA picture generated throughout this compile comprises timing violations and will produce practical errors if used. Confer with the Intel oneAPI DPC++ FPGA Optimization Information part on Timing Failures for extra data.

make[3]: *** [gzip.fpga] Error 42

make[3]: *** Deleting file ‘gzip.fpga’

make[2]: *** [src/CMakeFiles/gzip.fpga.dir/all] Error 2

make[1]: *** [src/CMakeFiles/fpga.dir/rule] Error 2

make: *** [fpga] Error 2

build_fpga.sh.o2515172:

Scanning dependencies of goal gzip.fpga

[ 16%] Constructing CXX object src/CMakeFiles/gzip.fpga.dir/gzip.cpp.o

[ 33%] Constructing CXX object src/CMakeFiles/gzip.fpga.dir/crc32.cpp.o

[ 50%] Constructing CXX object src/CMakeFiles/gzip.fpga.dir/WriteGzip.cpp.o

[ 66%] Constructing CXX object src/CMakeFiles/gzip.fpga.dir/CompareGzip.cpp.o

[ 83%] Constructing CXX object src/CMakeFiles/gzip.fpga.dir/gzipkernel.cpp.o

[100%] Linking CXX executable ../gzip.fpga

warning: -reuse-exe file ‘/residence/u208539/oneAPI-samples/DirectProgramming/C++SYCL_FPGA/ReferenceDesigns/gzip/construct/gzip.fpga’ not discovered; ignored

aoc: Compiling for FPGA. This course of might take a number of hours to finish. Previous to performing this compile, be sure you examine the experiences to make sure the design will meet your efficiency targets. If the experiences point out efficiency targets should not being met, code edits could also be required. Please discuss with the oneAPI FPGA Optimization Information for data on efficiency tuning functions for FPGAs.

aoc: Warning: A timing failure has been detected within the outputted binary. There was 1 timing violation,

which was a Setup failure of 35ps on clock:

u0|dcp_iopll|dcp_iopll_clk2x

Contemplate doing a number of of the next:

– Recompiling with a unique seed (utilizing -Xsseed=<S>).

– Lowering the world utilization of your design.

– If you’re utilizing a customized BSP, focus on the failure along with your BSP vendor.

src/CMakeFiles/gzip.fpga.dir/construct.make:198: recipe for goal ‘gzip.fpga’ failed

CMakeFiles/Makefile2:126: recipe for goal ‘src/CMakeFiles/gzip.fpga.dir/all’ failed

CMakeFiles/Makefile2:101: recipe for goal ‘src/CMakeFiles/fpga.dir/rule’ failed

Makefile:118: recipe for goal ‘fpga’ failed

wanyu

.

[ad_2]