[ad_1]

Hey!

I’ve developed a FPGA software program (NB: I am undecided it may be referred to as software program, however anyway

verilog code), about 2+ years in the past. Because it wanted a sinewave, I used coefficients saved in a

double entry ROM. 1024 coefficients, 18-bit. This could yield (and I feel it did at the moment)

18 kbits reminiscence utilization. See the next code.

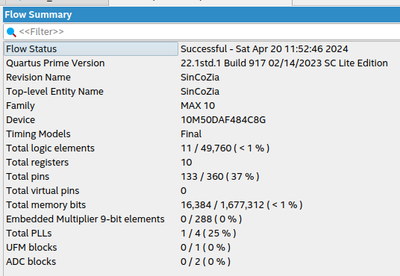

Now when compiling that code, the reminiscence utilization is 16k (16384 bits to be correct).

Might anyone clarify me what’s flawed and the best way to repair it?

Greatest regards,

Pascal

———— DA ROM —————

// Quartus Prime Verilog Template

// Twin Port ROM

module sine_rom

//#(parameter DATA_WIDTH=`ROM_DATW-1, parameter ADDR_WIDTH=`ROM_ADDW)

#(parameter DATA_WIDTH=18, parameter ADDR_WIDTH=10) (

enter [(ADDR_WIDTH-1):0] addr_a, addr_b,

enter clk,

output reg signed[(DATA_WIDTH-1):0] q_a, q_b

);

// Declare the ROM variable

reg signed[DATA_WIDTH-1:0] rom[2**ADDR_WIDTH-1:0]; // 18 * 1024 on this case

preliminary

start

$readmemh(“SineFiles/sine18_1ks.hex”, rom);

finish

at all times @ (posedge clk)

start

q_a <= rom[addr_a];

q_b <= rom[addr_b];

finish

endmodule

———————————–

[ad_2]