[ad_1]

Observe: This text is an English translation of this Japanese article. Please seek advice from the unique article for updates.

On this “Intel® FPGA Introduction Calendar 2021”, varied articles have highlighted the RISC-V model of the Smooth CPU Core, generally known as the Nios® V processor (hereinafter known as Nios V), which is now included in Intel® Quartus® Prime Professional Version 21.3 (hereafter QuartusPro v21.3). Together with this introduction, OpenOCD has been applied because the debugging mechanism for Nios V. It raises the query: Might OpenOCD be used for JTAG debugging with USB Blaster, not only for Nios V however for different CPUs as properly? This text explores that risk.

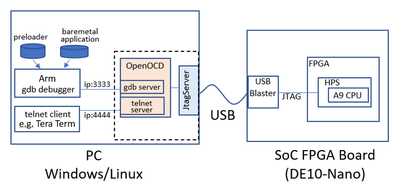

The experiment performed targeted on the CPU (Arm Cortex-A9) of the Cyclone® V SoC FPGA1. This part contains the OpenOCD configuration file for connecting to the Cyclone V SoC, together with gdb debugger scripts for downloading and executing code, and a TCL script for telnet connection.

OpenOCD, brief for Open On-Chip Debugger, is an “Open Supply software program aimed toward offering debugging, in-system programming, and boundary-scan for embedded gadgets.”2 It incorporates options of a gdb server and a telnet server, supporting a wide range of debug probes, thereby enabling debugging on quite a few embedded gadgets. The essential utilization includes working OpenOCD as a server within the background, appearing as an middleman to facilitate connections between shopper software program (like gdb or telnet shoppers) and the debug probe.

The model of OpenOCD included in QuartusPro v21.3 helps USB Blaster, permitting JTAG debugging through gdb debugger, concentrating on not simply Nios V however probably different CPUs as properly, equivalent to Arm Cortex-A9. This part delves into the investigation and testing of this functionality.

For organising OpenOCD, on Home windows, the set up of QuartusPro v21.3 is required. On Linux, putting in solely the Programmer of QuartusPro v21.3 suffices for utilizing OpenOCD. No extra set up of the Nios V toolchain is critical. Moreover, OpenOCD is offered to be used freed from cost, with out the necessity for a paid license.

This part outlines the examined configuration.

{Hardware}: The debugger PC and the FPGA board are related through JTAG (really utilizing an OnBoard USB Blaster, so a USB cable). The PC could be both Home windows or Linux.

PC Software program: OpenOCD is stored working, with the gdb server accessing the USB Blaster being lively. The gdb debugger for Arm CPU is related to the OpenOCD gdb server to facilitate debugging, which incorporates code downloading and execution.

The Terasic DE10-Nano equipment, outfitted with the Cyclone V SoC, was used for the experiment.

To start out OpenOCD, the Nios V Command Shell from Quartus v21.3 is used.

Initially, it’s a necessity to confirm whether or not the USB Blaster of the DE10-Nano equipment is appropriately acknowledged by the PC as a JTAG machine and if the HPS and FPGA are detected. This includes connecting the J13 of the DE10-nano to the PC utilizing a mini-USB cable with out an SD card inserted, after which powering on the DE10-nano. Following this, the jtagconfig command is executed.

[niosv-shell] C:intelFPGA_pro21.3> jtagconfig

1) DE-SoC [USB-1]

4BA00477 SOCVHPS

02D020DD 5CSEBA6(.|ES)/5CSEMA6/..

If this show seems, it’s regular. It confirms the JTAG ID of the HPS containing the Arm CPU as 4BA00477 (the identical as in Arria10’s HPS).

Creating OpenOCD Configuration File

To make use of OpenOCD, a configuration file detailing the goal setting is required. The format adheres to TCL. Initially, reference recordsdata throughout the set up folder of QuartusPro v21.3 are sought. Throughout the folder named

<install_folder>/quartus/bin64/oocd/openocd/scripts/board

there’s a file named

altera_arria10__aji_client.cfg.

It seems to be a configuration file for connecting to the HPS of Arria10 SoC, as inferred from its title and feedback. Utilizing this as a reference, a profitable connection to the goal Cyclone V SoC was established. The configuration file is as follows, named cyclone5_client.cfg.

###############################################################

# Level: Specify aji_client because the Driver

adapter driver aji_client

###############################################################

# Chip Title: Could be modified to any title you like (let's hold it as cvsoc)

set _CHIPNAME cvsoc

###############################################################

# JTAG ID of HPS TAP (Take a look at Entry Port)/DAP (Debug Entry Port)

set _DAP_TAPID 0x4ba00477

###############################################################

# Declare HPS DAP because the JTAG TAP (Take a look at Entry Port)

jtag newtap $_CHIPNAME cpu -irlen 4 -expected-id $_DAP_TAPID

###############################################################

# Declare that the HPS TAP is an ARM DAP (Debug Entry Port).

# Do that when ARMv6-M, ARMv7, ARMv8 are the targets

dap create $_CHIPNAME.dap -chain-position $_CHIPNAME.cpu

###############################################################

# The goal to be operated by the gdb debugger can be core0 of the HPS DAP

goal create $_CHIPNAME.cpu.0 cortex_a -dap $_CHIPNAME.dap -coreid 0 -dbgbase 0x80110000

After a number of trials and errors, the file was finally lowered to solely the important elements from the unique Arria10 file. One addition, within the final line of goal create…, is -dbgbase 0x80110003.

Launching and Verifying OpenOCD

The Nios V Command Shell of v21.3 is began. On this Shell, after altering the listing to the place the cyclone5_client.cfg file was saved, execute openocd -f cyclone5_client.cfg. Subsequently, the next log seems, after which the log show stops.

[niosv-shell] C:de10nanoOpenOCD_download> openocd -f cyclone5_client.cfg

Open On-Chip Debugger 0.11.0-R21.3

Licensed beneath GNU GPL v2

...[omitted for brevity]...

Information : Listening on port 4444 for telnet connections

...[omitted for brevity]...

Information : At current, The primary {hardware} cable can be used [1 cable(s) detected]

Information : Cable 1: device_name=(null), hw_name=DE-SoC, server=(null), port=USB-1, chain_id=0000019c3ca88620, persistent_id=1, chain_type=1, options=2048, server_version_info=Model 21.1.0 Construct 842 10/21/2021 SJ Customary Version

Information : TAP place 0 (4BA00477) has 0 SLD nodes

Information : TAP place 1 (2D020DD) has 0 SLD nodes

Information : Found 2 TAP gadgets

Information : Detected machine (tap_position=0) device_id=4ba00477, instruction_length=4, options=0, device_name=SOCVHPS

Information : Discovered a ARM machine at tap_position 0. At the moment assume it's JTAG-DP succesful

Information : Detected machine (tap_position=1) device_id=02d020dd, instruction_length=10, options=4, device_name=5CSEBA6(.|ES)/5CSEMA6/..

Information : Discovered an Intel machine at tap_position 1.At the moment assuming it's SLD Hub

Information : This adapter does not assist configurable velocity

Information : JTAG faucet: cvsoc.cpu faucet/machine discovered: 0x4ba00477 (mfg: 0x23b (ARM Ltd), half: 0xba00, ver: 0x4)

Information : JTAG faucet: auto0.faucet faucet/machine discovered: 0x02d020dd (mfg: 0x06e (Altera), half: 0x2d02, ver: 0x0)

Warn : AUTO auto0.faucet - use "jtag newtap auto0 faucet -irlen 10 -expected-id 0x02d020dd"

...[omitted for brevity]...

Information : beginning gdb server for cvsoc.cpu.0 on 3333

Information : Listening on port 3333 for gdb connections

From the primary half of the log, it is evident that the telnet server has began, ready for connections on port 4444. The latter half, starting with “Information: JTAG faucet:”, signifies that the machine ID has been appropriately acknowledged. Moreover, from the final two strains, it may be seen that the gdb server has been efficiently launched and is ready for connections on port 3333, confirming a profitable connection to the Cyclone V HPS gdb server.

By the best way, the “Warn: AUTO auto0.faucet…” message that seems in between signifies that the FPGA’s JTAG TAP definition was omitted within the cyclone5_client.cfg file, main the device to robotically detect it. The JTAG instruction size and different particulars are additionally auto-detected.

Now that OpenOCD has been efficiently launched, the subsequent step is to attach it with the gdb debugger.

Beginning and Verifying gdb

The gdb debugger is initiated and related to the OpenOCD gdb server. Right here, the Arm gdb included with SoCEDS v18.1 commonplace version is used (typically, any gdb supporting the goal CPU ought to work, however there are considerations that if an ELF file is learn by gdb, the image desk may not be loaded appropriately until the gdb model matches the gcc toolchain that created the ELF). A number of causes for utilizing v18.1 embrace:

- The pattern HW design for DE10-nano compiles with out points (as much as v18.1, the pattern containing FrameReader Video IP could be compiled).

- There isn’t any must obtain & set up Cygwin or WSL individually, amongst different causes4.

The SoCEDS command shell is launched, and from there, the arm-altera-eabi-gdb for Arm is began. It is essential to incorporate the choice for connecting to OpenOCD’s gdb server on port 3333 at this stage.

arm-altera-eabi-gdb -ex ‘goal extended-remote localhost:3333’

$ arm-altera-eabi-gdb -ex 'goal extended-remote localhost:3333'

GNU gdb (Sourcery CodeBench Lite 2016.11-88) 7.11.1.20160608-git

Copyright (C) 2016 Free Software program Basis, Inc.

...[omitted for brevity]...

Distant debugging utilizing localhost:3333

warning: No executable has been specified and goal doesn't assist

figuring out executable robotically. Attempt utilizing the "file" command.

0x00002fa8 in ?? ()

(gdb)

The gdb server is efficiently related on localhost:3333, and the CPU is stopped at tackle 0x00002fa8. This additionally provides a couple of strains of messages to the Nios V command shell that’s working OpenOCD (examples are omitted right here).

Subsequent, to see if the state of the Arm CPU is seen, the data reg command is used to examine.

(gdb) information reg

r0 0x0 0

r1 0x0 0

r2 0xfffffee0 4294967008

r3 0xff704000 4285546496

r4 0x77857713 2005235475

r5 0xffd02000 4291829760

r6 0x76 118

r7 0xfffff014 4294963220

r8 0xfffff014 4294963220

r9 0x76 118

r10 0xffd02000 4291829760

r11 0xffd02000 4291829760

r12 0xa0002041 2684362817

sp 0xfffffed0 0xfffffed0

lr 0x3104 0x3104

laptop 0x2fa8 0x2fa8

cpsr 0x600001d3 1610613203

(gdb)

All register contents are efficiently verified.

Attempting the print command for system reminiscence entry can be explored. Right here, the crc register of the System Supervisor, mapped at tackle 0xffd080f0, is accessed.

(gdb) print/x *0xffd080f0

$1 = 0xe763552a

(gdb)

As per the Cyclone V SoC documentation, the worth is at its preliminary state after a chilly reset, which is 0xE763552A.

This confirms that each one primary gdb instructions are functioning appropriately!

To exit gdb, use the ‘q’ command. Additionally, terminate OpenOCD by inputting Ctrl-C.

Obtain and Run Script with gdb

Now, let’s proceed to the ultimate objective of this text: downloading and working code utilizing gdb scripts. Under are some script examples, tailor-made to the file format and model of the preloader. Mainly, changing the contents of the scripts (*.ds) offered for Arm DS (or Arm DS-5) to gdb format will suffice.

ELF Format Preloader (v2013.01)

First, a script for downloading and executing an ELF format file of the preloader model 2013.01. For a very long time (till SoCEDS v18.1), the preloader (u-boot) code included with SoCEDS was of model 2013.01. The script instance for downloading and executing the ensuing ELF format file (spl/u-boot-spl) on the goal machine (DE10-Nano’s Cyclone V SoC) is as follows (created as download_preloader_elf.gdb):

set verify off

set pagination off

restore

symbol-file -readnow

thbreak spl_boot_device

bounce _start

#Cease watchdog timer

#permodrst Reg , reset watch canine timer

#set $permodrst = (int *)0xffd05014

#set *$permodrst = (*$permodrst) | (1<<6)

#set *$permodrst = (*$permodrst) & ~(1<<6)

[Explanation of the Script] The important thing level right here is setting a breakpoint on the operate spl_boot_device. This operate checks the place the preloader will load the subsequent Utility picture from (SD card or QSPI or NAND). When this level is reached, all essential initializations for booting are accomplished, and the debugger stops right here (additional execution will lead to an error as no SD card is inserted). Most often, the subsequent step could be to obtain and debug the Utility. The ultimate three strains (set …), that are commented out, are supposed to cease the WatchDog timer began by the preloader. They toggle the reset little bit of the WatchDogTimer0 within the reset supervisor to cease WatchDogTimer0. If extra duties, like working an Utility, are to be carried out afterward, the WatchDog timer, if left working, would possibly trigger a reset because of a timeout (resulting in an sudden reset). To stop this, uncomment these final three strains.

This script is executed utilizing the -x possibility with gdb.

arm-altera-eabi-gdb -ex ‘goal extended-remote localhost:3333’ -x download_preloader_elf.gdb

Vital: Earlier than working this gdb command, please restart the DE10-Nano board5 and restart OpenOCD.

$ arm-altera-eabi-gdb -ex 'goal extended-remote localhost:3333' -x download_preloader.gdb

GNU gdb (Sourcery CodeBench Lite 2016.11-88) 7.11.1.20160608-git

Copyright (C) 2016 Free Software program Basis, Inc.

License GPLv3+: GNU GPL model 3 or later <http://gnu.org/licenses/gpl.html>

...[omitted for brevity]...

Distant debugging utilizing localhost:3333

warning: No executable has been specified and goal doesn't assist

figuring out executable robotically. Attempt utilizing the "file" command.

0x00002fa4 in ?? ()

Restoring part .textual content (0xffff0000 to 0xffff6968)

Restoring part .rodata (0xffff6968 to 0xffff81f0)

Restoring part .information (0xffff81f0 to 0xffff90c4)

{Hardware} assisted breakpoint 1 at 0xffff1342

cvsoc.cpu.0 rev 0, partnum c09, arch f, variant 3, implementor 41

Non permanent breakpoint 1, 0xffff1342 in spl_boot_device ()

(gdb)

When executing this command, in case you have the DE10-Nano’s serial terminal open, the next show happens, confirming that the preloader is executed:

U-Boot SPL 2013.01.01 (Dec 14 2021 - 13:59:40)

BOARD : Altera SOCFPGA Cyclone V Board

...[omitted for brevity]...

INFO : Watchdog enabled

SDRAM: Initializing MMR registers

SDRAM: Calibrating PHY

SEQ.C: Getting ready to start out reminiscence calibration

SEQ.C: CALIBRATION PASSED

SDRAM: 1024 MiB

ELF Format Preloader (v2021.04 and Later)

Preloader, primarily based on the u-boot code, has undergone modifications since model 2021.04 to incorporate machine tree recordsdata. Consequently, the debugger obtain script has additionally wanted to be modified. Under is the up to date script:

set verify off

set pagination off

restore

symbol-file -readnow

restore u-boot-spl.dtb binary &__bss_end

thbreak spl_boot_device

bounce _start

#Cease watchdog timer

#permodrst Reg , reset watch canine timer

#set $permodrst = (int *)0xffd05014

#set *$permodrst = (*$permodrst) | (1<<6)

#set *$permodrst = (*$permodrst) & ~(1<<6)

Rationalization of the Script The brand new preloader (u-boot) requires loading each the ELF file and the machine tree (.dtb) into reminiscence. The road restore u-boot-spl.dtb binary &__bss_end masses the machine tree. __bss_end is the tip tackle of the preloader code, and the .dtb is positioned instantly after it in reminiscence, as per the specs of this model of preloader (u-boot).

Binary Format Preloader-mkpimage.bin

This script is used to execute the preloader utilizing the binary format file preloader-mkpimage.bin, supposed for writing to a boot SD card. (This file comes included with the pattern design DE10_NANO_SoC_GHRD folder offered by Terasic, helpful for many who need a fast operational examine). The script may also launch the preloader binary file u-boot-splx4.sfp, created for newer variations (later than 2013.xx) of boot media.

set verify off

set pagination off

restore binary 0xffff0000 0x0 0xefff

watch *0xff704004

bounce *0xffff004c

#Cease watchdog timer

#permodrst Reg , reset watch canine timer

#set $permodrst = (int *)0xffd05014

#set *$permodrst = (*$permodrst) | (1<<6)

#set *$permodrst = (*$permodrst) & ~(1<<6)

Rationalization of the Script The important thing level is specifying the reminiscence offset tackle (0xffff0000) for writing the binary, the beginning (0x0), and the tip place (0xefff) of the binary file within the restore command. The reminiscence offset tackle (0xffff0000) is the beginning tackle of the HPS OnChipMemory. The beginning of the binary file is from the start (0x0), and the tip is the utmost measurement of the preloader code, 0xefff. A watch level (triggered on specified reminiscence entry) is used to cease the preloader since it is a binary code with out image info. The watch level is about to halt the CPU when the SD card controller is accessed for studying/writing. 0xff704004 is the tackle of a register within the SD card controller. The execution begin tackle is 0xffff004c, as specified by the binary format and bootrom specs.

Downloading and Working Preloader/Baremetal App

As a extra sensible instance, this script masses and executes the preloader, adopted by a pattern Baremetal utility.

set verify off

set pagination off

restore <u-boot-splのpath>

symbol-file -readnow <u-boot-splのpath>

thbreak spl_boot_device

bounce _start

#Cease watchdog timer

#permodrst Reg , reset watch canine timer

set $permodrst = (int *)0xffd05014

set *$permodrst = (*$permodrst) | (1<<6)

set *$permodrst = (*$permodrst) & ~(1<<6)

# load and run Utility

restore <utility elf path>

symbol-file -readnow <utility elf path>

bounce _start

Rationalization of the Script: This script provides instructions to obtain and execute an utility ELF file (.axf) to the beforehand launched script for downloading the preloader. After executing the preloader, a course of to cease the WatchDog Timer is enabled. Ideally, this course of to cease the WatchDog Timer needs to be carried out initially of the applying. Since this course of will not be included within the Software program Examples supplied with SoCEDS, it is included right here. Warning When Constructing the Software program Instance Included with SoCEDS: This time, I attempted compiling and verifying the operation of the Software program Instance included with SoCEDS v18.1, particularly the Altera-SoCFPGA-HardwareLib-16550-CV-GNU (/embedded/examples/software program/Altera-SoCFPGA-HardwareLib-16550-CV-GNU). Some factors to notice: the unique pattern code is meant to be executed utilizing an Arm debugger and is about as much as show printf output on the debugger’s console (utilizing a characteristic known as semi-hosting). With the gdb debugger, this characteristic must be turned off. For this function, line 46 of the Makefile was modified to LINKER_SCRIPT := cycloneV-dk-ram.ld.

Now, let’s attempt connecting to OpenOCD utilizing telnet. With a telnet shopper, one can immediately execute instructions supported by OpenOCD6. Moreover, a TCL interpreter known as Jim-Tcl runs because the command-line interface, enabling the execution of TCL scripts.

First, be certain that OpenOCD is working. By default, OpenOCD’s telnet server waits for connections on port 4444.

The next picture exhibits an instance utilizing Tera Time period because the Telnet shopper. To start out, configure the settings as proven within the determine: Host: localhost, Service: Telnet, TCP port#: 4444, and click on “OK”.

After a couple of seconds, if you happen to see textual content output from OpenOCD and a immediate for command enter, the connection is profitable.

Open On-Chip Debugger

>

Concurrently, the next log needs to be added to the Shell window the place OpenOCD is working.

Information : accepting 'telnet' connection on tcp/4444

Subsequent, this is an instance of executing three OpenOCD instructions associated to CPU debugging (halt, reg, mdw).

> # Halt CPU

> halt

cvsoc.cpu.0 rev 0, partnum c09, arch f, variant 3, implementor 41

goal halted in ARM state because of debug-request, present mode: Supervisor

cpsr: 0x600f0153 laptop: 0x00101fac

MMU: disabled, D-Cache: disabled, I-Cache: enabled

>

>

> # print registers

> reg

===== ARM registers

(0) r0 (/32): 0x3fffdfa4 (soiled)

(1) r1 (/32): 0x3fffd300 (soiled)

(2) r2 (/32): 0x00000200

(3) r3 (/32): 0x00000000

(4) r4 (/32): 0x00000000

(5) r5 (/32): 0x00000000

(6) r6 (/32): 0x00000076

(7) r7 (/32): 0xfffff014

(8) r8 (/32): 0xffffffff

(9) r9 (/32): 0x00000005

(10) r10 (/32): 0xffd02000

(11) r11 (/32): 0x3fffd2ec

(12) r12 (/32): 0xffffffff

(13) sp_usr (/32)

(14) lr_usr (/32)

(15) laptop (/32): 0x00101fac

(16) r8_fiq (/32)

(17) r9_fiq (/32)

...[omitted for brevity]...

(73) d29 (/64)

(74) d30 (/64

>

> # Learn a reminiscence mapped register

> mdw 0xffd05014

0xffd05014: 01b6c035

Moreover, let’s examine different OpenOCD instructions equivalent to “`scan_chain“` and “`dap information“`.

> scan_chain

TapName Enabled IdCode Anticipated IrLen IrCap IrMask

-- ------------------- -------- ---------- ---------- ----- ----- ------

0 cvsoc.cpu Y 0x4ba00477 0x4ba00477 4 0x01 0x03

1 auto0.faucet Y 0x02d020dd 0x00000000 10 0x01 0x03

> dap information

DAP transaction stalled (WAIT) - slowing down

AP ID register 0x24770002

Sort is MEM-AP APB

MEM-AP BASE 0x80000000

ROM desk in legacy format

Part base tackle 0x80000000

Peripheral ID 0x00000ee001

Designer is 0x0ee, Altera

Half is 0x1, Unrecognized

Part class is 0x1, ROM desk

MEMTYPE system reminiscence not current: devoted debug bus

ROMTABLE[0x0] = 0x1003

Part base tackle 0x80001000

Peripheral ID 0x04001bb961

Designer is 0x4bb, ARM Ltd

Half is 0x961, CoreSight TMC (Hint Reminiscence Controller)

Part class is 0x9, CoreSight part

Sort is 0x32, Hint Hyperlink, FIFO, buffer

...[omitted for brevity]...

[L01] ROMTABLE[0x20] = 0x0

[L01] Finish of ROM desk

ROMTABLE[0x24] = 0x0

Finish of ROM desk

>

The dap information command shows an inventory of the contents of the Arm CoreSight DAP’s ROM desk.

Downloading and Working the Preloader/Baremetal App

A TCL script has been written to obtain and run each the preloader and a baremetal utility. As famous within the file’s feedback, in contrast to with gdb, one wants to find out the symbol-to-address mapping upfront7. As soon as saved as ‘download_preloader_app.tcl’, it may be executed from the OpenOCD immediate within the telnet terminal utilizing supply download_preloader_app.tcl. Ensure that to regulate the elements enclosed in […] to suit your setting. Observe that if a relative path is specified for the file path, it needs to be relative to the present working listing of the Shell the place OpenOCD is launched.

Equally to gdb, earlier than executing via the telnet connection, restart the DE10-Nano board5 and restart OpenOCD.

halt

###################################################################

# Obtain the Preloader

# Specify utilizing a relative path from the pwd of the shell the place OpenOCD was launched.

load_image [path to preloader's elf file]

###################################################################

# Setting the Begin Tackle for Execution

reg laptop 0xffff0000

###################################################################

# Set a breakpoint on the spl_boot_device operate within the preloader

# Instance of the best way to discover this tackle:

# $ arm-altera-eabi-readelf.exe -s [path to preloader elf file] | grep spl_boot_device

#

bp [address of spl_boot_device function] 2 hw

###################################################################

# Execute the preloader

resume

wait_halt

###################################################################

# Reset the WatchDog Timer

set permodrst 0xffd05014

set permodrst_val "0x"[lindex [mdw $permodrst] 1]

mww $permodrst [expr ($permodrst_val)|(1<<6)]

mww $permodrst $permodrst_val

###################################################################

# Load the Baremetal Utility

load_image [path to application elf]

###################################################################

# The way to discover the beginning tackle of the applying

# (for SOCEDS bundled Altera-SoCFPGA-HardwareLib-16550-CV-GNU)

# arm-altera-eabi-readelf.exe -s [path to application elf] | grep _start

reg laptop [start address of application]

###################################################################

# Clear Thumb2 Mode

# cpsr bit-5 : Thumb execution state bit - to be cleared

set cpsr_val [lindex [reg cpsr] 2]

reg cpsr [expr ($cpsr_val)&(~(1<<5)&0xffffffff)]

###################################################################

# Execute the applying

resume

It has been confirmed that with OpenOCD included in QuartusPro v21.3, code obtain and execution to the Arm Cortex-A9 CPU of Cyclone V SoC is feasible through gdb and telnet connections.

It is now possible to carry out JTAG Debugging for Intel SoC FPGAs, which beforehand required a paid license, with free instruments.

After all, paid debuggers excel by way of code obtain velocity and GUI setting8.

Whereas “official documentation assist remains to be anticipated,” it’s hoped that when the assist paperwork are launched, there can be enhancements in usability and enhanced options.

Though the title OpenOCD was considerably acquainted, it had not been used till now. Nevertheless, the chance arose with the inclusion of precompiled binaries within the device, prompting an early trial.

First impressions are:

- JTAG debugging with gdb is handy and easy.

- Telnet connection seems promising for varied operations round JTAG. It additionally appears handy when mixed with Tera Time period’s macros.

- The supply code can be obtainable on GitHub (see References), which might be attention-grabbing for fanatics.

That is the final feeling.

Thanks. (Feedback and suggestions are welcome!)

Intel applied sciences might require enabled {hardware}, software program, or service activation.

No product or part could be completely safe.

Your prices and outcomes might fluctuate.

© Intel Company. Intel, the Intel brand, and different Intel marks are emblems of Intel Company or its subsidiaries. Different names and types could also be claimed because the property of others.

The merchandise described might comprise design defects or errors generally known as errata which can trigger the product to deviate from revealed specs. Present characterised errata can be found on request.

Intel disclaims all specific and implied warranties, together with with out limitation, the implied warranties of merchantability, health for a selected function, and non-infringement, in addition to any guarantee arising from the course of efficiency, course of dealing, or utilization in commerce.

-

Whereas QuartusPro v21.3 doesn’t assist this machine, it was challenged because of the need to see it function on a fairly priced FPGA. ↩︎

-

From the official web site’s What’s OpenOCD part. ↩︎

-

Even with out this description, if the FPGA will not be configured, it’ll function by robotically detecting the dbgbase tackle at startup. The tackle detected robotically was displayed as Detected core 0 dbgbase: 80110000 when the debug possibility (-d) was used. Then again, if an IP (SLD Node) for JTAG is configured within the FPGA, computerized detection doesn’t work properly, and with out this feature, a startup error happens. ↩︎

-

With current variations of Home windows, the make of the preloader might lead to an error. One countermeasure is to set /usr/bin initially of the PATH setting variable with export PATH=/usr/bin:$PATH. ↩︎

-

Since a CPU reset command has not been discovered, handbook resetting of the goal is at the moment used instead. ↩︎ ↩︎

-

For detailed instructions, seek advice from the OpenOCD Consumer’s Information. Not all instructions are applied. ↩︎

-

If anybody is aware of a greater means, please share within the feedback m(–)m ↩︎

-

Combining with VSCode or Eclipse is likely to be potential for self-assembly. Utilizing VSCode+gdb+OpenOCD for ARM improvement generally is a reference. ↩︎

[ad_2]