[ad_1]

Hello, I need to use DSP to do the web checksum offloading. I need to do a+b+c (16 bits) in a single clock and I’m utilizing Agilex7 AGFB023R25A2E2V.

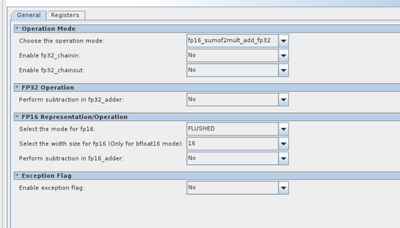

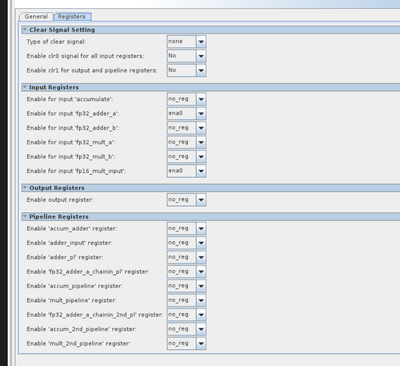

I chosen Native Floating Level DSP and configured to “Sum of two FP16 multiplication with FP32 addition mode” utilizing “fp16_mult_top_a*fp16_mult_top_b(16’b1) + fp16_mult_bot_a*fp16_mult_bot_b(16’b1) + fp32_adder_a”.

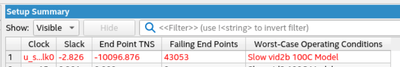

Nevertheless, the timing of my challenge modified from 0 ns to -2 ns with about 18 DSP enabled. Have you learnt find out how to configure the DSP to have a greater timing efficiency? Do I’ve a better option for the IP core?

[ad_2]